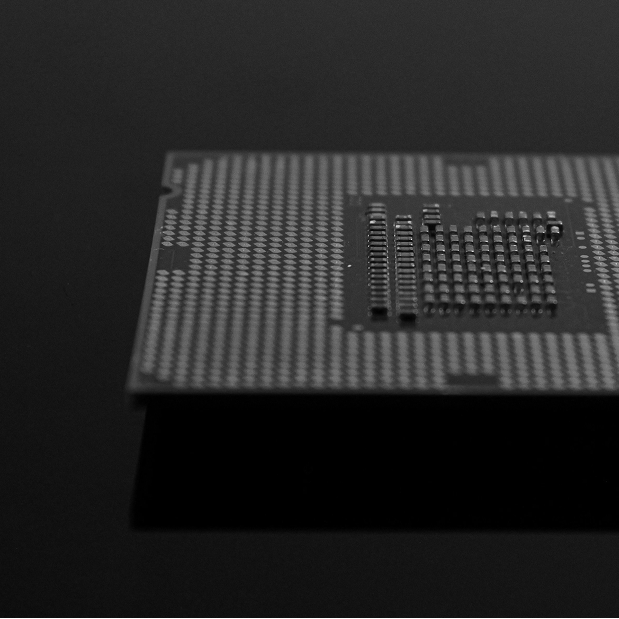

PUF IPs For Your SoC: Unique Device Identity

Hardware root keys without key injection. Digital and analog PUF options. Optimised for small silicon footprint.

Inside you’ll find:

- Full internal block diagram & Hardware integration guide

- Environmental and statistical performance across temperature range

- Performance Metrics

Architecture Summary

PUF IP Technical Highlights

-

Digital or Analog implementation options

-

128/256-bit seed

-

<30K gates fits constrained SoCs

-

Quantum derived

-

APB/AXI interface, customisable per SoC

- Optimised for us in open source RoTs (Caliptra/Opentitan)

Key Injection Doesn’t Scale

Factory provisioning is expensive, slow, and a supply chain risk. Every device that leaves the line with an injected key is a device that could have been compromised during manufacturing. And once keys are stored in NVM, they’re a target.

Keys Born in Silicon

Digital & Analog PUF IP, with Direct Engineering Support Included

- A PUF extracts a unique cryptographic fingerprint from your chip’s physical structure — no secrets stored, no injection needed.

- Integration guidance and compliance documentation included.

- From security architecture to and tape-out, expert support through every stage of silicon development including system certification.

Digital PUF

Logic-based entropy source array with fuzzy extractor. Optimised for small silicon footprint at <30K gates. Pure digital — no analog integration needed.

QDID PUF

Quantum tunnelling-based entropy. Side-channel protected by design. Multiple seeds available, no secret leakage on power-off. Proven on TSMC, GlobalFoundries & UMC.

Anti-Cloning & Attestation

Provision hardware-based identity for secure boot, device attestation and easily integrated into Caliptra/opentitan architectures.

Built For Security-Critical Silicon

Proven silicon IP and embedded software, built for real world scenarios.

Constrained SoCs & IoT

Physical AI & Next Generation Designs

Custom SoCs & Chiplets

Evaluate Our Digital & Analog PUF IP Architecture

Full PUF specifications, architecture diagrams and performance data in the product brief.